PWM

Overview

Pulse width modulation (PWM) is an efficient technique for controlling analog circuits using digital outputs from microprocessors.

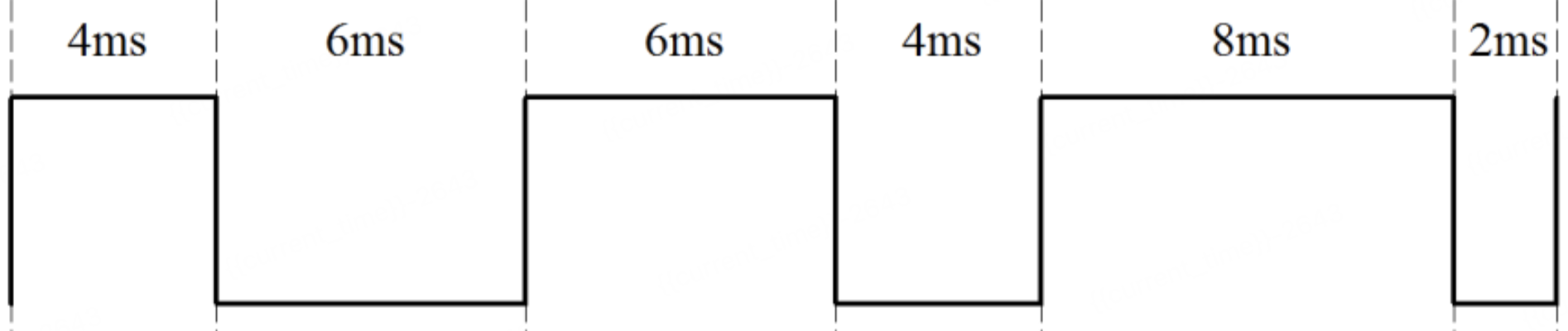

The figure above shows a PWM waveform with a 100 Hz periodic frequency, featuring a 40% high-level duty cycle and 60% low-level duty cycle. By adjusting the high-level duty cycle value, the analog output level can be modified.

API description

tkl_pwm_init

OPERATE_RET tkl_pwm_init(TUYA_PWM_NUM_E ch_id, CONST TUYA_PWM_BASE_CFG_T *cfg);

-

Features:

- Initialize the specified PWM instance using the port number and basic configuration, and return the initialization result.

-

Parameters:

-

ch_id: The channel ID. -

cfg: The basic PWM configuration, including output polarity, duty cycle, and frequency.typedef struct { TUYA_PWM_POLARITY_E polarity; TUYA_PWM_COUNT_E count_mode; //pulse duty cycle = duty / cycle; exp duty = 5000,cycle = 10000; pulse duty cycle = 50% UINT_T duty; UINT_T cycle; UINT_T frequency; // (bet: Hz) } TUYA_PWM_BASE_CFG_T; -

polarity:Name Definition TUYA_PWM_NEGATIVE The PWM low active output. TUYA_PWM_POSITIVE The PWM high active output. -

count_mode: The counting mode, includingTUYA_PWM_CNT_UPandTUYA_PWM_CNT_UP_AND_DOWN. -

duty: The duty cycle, used withcycle. Output =duty÷cycle. -

cycle: The cycle or granularity. Output =duty÷cycle. -

frequency: The output frequency, in Hz.

-

-

Return value:

OPRT_OK: Success.- For more information, see

tuya_error_code.h.

tkl_pwm_deinit

OPERATE_RET tkl_pwm_deinit(TUYA_PWM_NUM_E ch_id);

- Features:

- Deinitialize the PWM.

- This interface stops the ongoing transmission (if any) and releases the related software and hardware resources.

- Parameters:

ch_id: The channel ID.

- Return value:

OPRT_OK: Success.- For more information, see

tuya_error_code.h.

tkl_pwm_start

OPERATE_RET tkl_pwm_start(TUYA_PWM_NUM_E ch_id);

- Features:

- Start the PWM.

- Parameters:

ch_id: The channel ID.

- Return value:

OPRT_OK: Success.- For more information, see

tuya_error_code.h.

tkl_pwm_stop

OPERATE_RET tkl_pwm_stop(TUYA_PWM_NUM_E ch_id);

- Features:

- Stop the PWM.

- Parameters:

port: The port number.

- Return value:

OPRT_OK: Success.- For more information, see

tuya_error_code.h.

tkl_pwm_multichannel_start

OPERATE_RET tkl_pwm_multichannel_start(TUYA_PWM_NUM_E *ch_id, UINT8_T num);

- Features:

- Start multi-channel PWM simultaneously. This interface is used for multi-channel combined output in scenarios with strict timing requirements.

- Parameters:

ch_id: The list of channel IDs in the form of an array.num: The number of channels to be started.

- Return value:

OPRT_OK: Success.- For more information, see

tuya_error_code.h.

tkl_pwm_multichannel_stop

OPERATE_RET tkl_pwm_multichannel_stop(TUYA_PWM_NUM_E *ch_id, UINT8_T num);

-

Features:

- Stop multi-channel PWM simultaneously. This interface is used for multi-channel combined output in scenarios with strict timing requirements.

-

Parameters:

ch_id: The list of channel IDs in the form of an array.num: The number of channels to be stopped.

-

Return value:

OPRT_OK: Success.- For more information, see

tuya_error_code.h.

tkl_pwm_info_set

OPERATE_RET tkl_pwm_info_set(TUYA_PWM_NUM_E ch_id, CONST TUYA_PWM_BASE_CFG_T *info);

- Features:

- Set PWM configuration parameters. After PWM is started, the configuration can be modified dynamically, and then the PWM shall be started again.

- Parameters:

ch_id: The channel ID.info: The basic PWM configuration, including output polarity, duty cycle, and frequency. The struct parameters are as described above.

- Return value:

- An error message is returned on failure.

OPRT_OK: Success. - For more information, see

tuya_error_code.h.

- An error message is returned on failure.

tkl_pwm_info_get

OPERATE_RET tkl_pwm_info_get(TUYA_PWM_NUM_E ch_id, TUYA_PWM_BASE_CFG_T *info);

- Features:

- Get the PWM configuration information.

- Parameters:

ch_id: The channel ID.info: The basic PWM configuration, including output polarity, duty cycle, and frequency. The struct parameters are as described above.

- Return value:

- An error message is returned on failure.

OPRT_OK: Success. - For more information, see

tuya_error_code.h.

- An error message is returned on failure.

tkl_pwm_cap_start

OPERATE_RET tkl_pwm_cap_start(TUYA_PWM_NUM_E ch_id, CONST TUYA_PWM_CAP_IRQ_T *cfg);

-

Features:

- Enable the PWM input capture mode.

-

Parameters:

-

ch_id: The channel ID. -

cfg: The PWM input capture configuration, as detailed below.-

cap_mode:Name Definition TUYA_PWM_CAPTURE_MODE_ONCE Single trigger mode TUYA_PWM_CAPTURE_MODE_PERIOD Multiple trigger mode -

trigger_level:Name Definition TUYA_PWM_NEGATIVE The trigger signal is falling edge. TUYA_PWM_POSITIVE The trigger signal is rising edge. -

clk: The sampling clock of the captured signal. -

cb: The callback function of the captured signal.typedef VOID_T (*TUYA_PWM_IRQ_CB)(TUYA_PWM_NUM_E port, TUYA_PWM_CAPTURE_DATA_T data, VOID_T *arg);typedef struct { UINT_T cap_value; /* Captured data */ TUYA_PWM_POLARITY_E cap_edge; /* Capture edge, TUYA_PWM_NEGATIVE:falling edge, TUYA_PWM_POSITIVE:rising edge */ } TUYA_PWM_CAPTURE_DATA_T;

-

-

arg: The parameter of the callback function.

-

-

Return value:

- An error message is returned on failure.

OPRT_OK: Success. - For more information, see

tuya_error_code.h.

- An error message is returned on failure.

tkl_pwm_cap_stop

OPERATE_RET tkl_pwm_cap_stop(TUYA_PWM_NUM_E ch_id);

-

Features:

- Disable the PWM input capture mode.

-

Parameters:

ch_id: The channel ID.

-

Return value:

- An error message is returned on failure.

OPRT_OK: Success. - For more information, see

tuya_error_code.h.

- An error message is returned on failure.

Example

void tuya_pwm_test(void)

{

OPERATE_RET ret;

TUYA_PWM_BASE_CFG_T cfg = {.polarity = TUYA_PWM_POSITIVE,\

.duty = 1000,

.cycle = 10000,

.frequency = 1000};

ret = tkl_pwm_init(TUYA_PWM_NUM_0, &cfg);

if (ret != OPRT_OK) {

//Fail

return;

}

ret = tkl_pwm_start(TUYA_PWM_NUM_0);

if (ret != OPRT_OK) {

//Fail

return;

}

tkl_system_delay(5000);

ret = tkl_pwm_info_get(TUYA_PWM_NUM_0, &cfg);

if (ret != OPRT_OK) {

//Fail

return;

}

if(cfg.duty !=5000){

cfg.duty =5000;

}

ret = tkl_pwm_info_set(TUYA_PWM_NUM_0, &cfg);

//Delay

tkl_system_delay(5000);

ret = tkl_pwm_stop(TUYA_PWM_NUM_0);

if (ret != OPRT_OK) {

//Fail

return;

}

ret = tkl_pwm_deinit(TKL_PWM1_CH);

if (ret != OPRT_OK) {

//Fail

return;

}

}

Is this page helpful?

YesFeedbackIs this page helpful?

YesFeedback